# An Efficient Interpreter for Soufflé

# XIAOWEN HU SID: 460048664

Supervisor: A.Prof Bernhard Scholz

This thesis is submitted in partial fulfillment of the requirements for the degree of Bachelor of Information Technology (Honours)

> School of Information Technologies The University of Sydney Australia

> > 17 July 2020

## **Student Plagiarism: Compliance Statement**

I certify that:

I have read and understood the University of Sydney Student Plagiarism: Coursework Policy and Procedure;

I understand that failure to comply with the Student Plagiarism: Coursework Policy and Procedure can lead to the University commencing proceedings against me for potential student misconduct under Chapter 8 of the University of Sydney By-Law 1999 (as amended);

This Work is substantially my own, and to the extent that any part of this Work is not my own I have indicated that it is not my own by Acknowledging the Source of that part or those parts of the Work.

Name: Xiaowen Hu

Signature:

Date:

#### Abstract

Soufflé is a highly efficient logic engine that is used in various applications, including static program analysis, (de-)compiler tools, network analysis, and data analytics. Soufflé obtains high performance by synthesising parallel C++ from logic code. However, compilation of Soufflé can often takes several minutes, which slows down the development cycle. As a result, an efficient interpreter is desired to speed up the debugging and development process.

This work investigates various techniques to implement high-performance interpreters for Soufflé so that the performance gap between interpreted Soufflé and synthesised C++ Soufflé code can be improved. Inherently, the interpreter will always be substantially slower than the synthesised C++ code due to dispatch of instructions and virtualisation layers of data-structures. In this work, we enable high-efficient, parallel data structures in the interpreter by adding virtual adapter techniques on the statically typed data structure which could not be used during runtime in prior. We also present a new strategy for implementing a tree-walk interpreter - the *Switch-based Shadow Tree* technique. The new technique ensures a high-performance tree-walk interpreter for a coarse-grained instruction set and has sound engineering principles for the ease of development. In this work, we implement two different interpreters for Soufflé, and contrast their performance characteristics: the Soufflé's Tree Interpreter (STI) with our new Switch-based Shadow Tree technique, and a Soufflé Virtual Machine (SVM) with a standard virtual machine. STI follows better software engineering principles, easing the maintenance and future-proofs the interpreter for extensions.

We conduct experiments with real-world applications, and show that our new Switch-based Shadow Tree technique outperforms the legacy interpreter of Soufflé, which cannot complete its computation due to memory depletion and time-outs on some benchmarks. We also show that STI is only 2.11 - 5.88 times slower than the synthesised C++ code, and it is faster than SVM. We also provide a performance model that explains the gap between the synthesised C++ code and the interpreted execution of logic programs.

## Acknowledgements

First of all, most enormous thank to my supervisor Bernhard Scholz. Thank you for being so patient and supportive, and thank you for helping me out, not only in academic but also in my personal life, I could not make it without you. It was such an enjoyable and pleasant experience working with you.

I also want to thank Herbert Jordan for helping me with this project, you have so many great ideas and I've learnt a lot from you; and thank you to Martin McGrane, for reviewing and refactoring my code, made me a better programmer.

I'd also like to thank Abdul Zreika, David Zhao, Ge Jin, Herbert Jordan, and Jiajun Huang for proofreading my thesis and providing valuable opinions. Especially to Abdul and David, for offering detailed feedback and helping on the wording and grammars. You guys are so kind, and I really appreciate it.

To Ruran Jin, thank you for keeping me company and supporting me throughout those years. To my lovely friends, Xinping Miao, Huamiao Xue, Tianhao Yu, Ding Zhang, Hang Li, Qi Sheng, Zezhou Chen, Jiajun Huang, Ge Jin, Greg Ge, Dawei Tao and others, thank you for having my back and believing in me. I wish all of you all the best.

Finally, I want to thank my wonderful family. It was a very rough year, but I'm glad you were there for me.

## CONTENTS

| Student Plagiarism: Compliance Statement                        | ii   |

|-----------------------------------------------------------------|------|

| Abstract                                                        | iii  |

| Acknowledgements                                                | iv   |

| List of Figures                                                 | viii |

| List of Tables                                                  | X    |

| Chapter 1 Introduction                                          | 1    |

| 1.1 Contributions                                               | 4    |

| 1.1.1 Outline                                                   | 5    |

| Chapter 2 Soufflé                                               | 6    |

| 2.1 Logic Programming                                           | 6    |

| 2.1.1 Basic Structure of Logic Programs                         | 6    |

| 2.2 Overview of Soufflé                                         | 7    |

| 2.2.1 The RAM Language                                          | 8    |

| 2.2.2 Example                                                   | 10   |

| 2.3 Chapter Summary                                             | 12   |

| Chapter 3 Background and Related Work: Interpreter and Dispatch | 13   |

| 3.1 Overview                                                    | 13   |

| 3.2 Interpreter                                                 | 13   |

| 3.3 Abstract Syntax Tree Interpreter                            | 14   |

| 3.3.1 Virtual Function and Visitor Pattern                      | 15   |

| 3.3.2 Switch Dispatch                                           | 15   |

| 3.4 Virtual Machine Interpreter                                 | 16   |

| 3.4.1 Stack-based VM                                            | 17   |

| 3.4.2 Register-based VM                                         | 17   |

|      |        | Contents                                | vi |

|------|--------|-----------------------------------------|----|

|      | 3.4.3  | Stack-based VM versus Register-based VM | 18 |

| 3.5  | Dispa  | atch Techniques                         | 19 |

|      | 3.5.1  | Branch Prediction and Context Problem   | 19 |

|      | 3.5.2  | Central Dispatch                        | 20 |

|      | 3.5.3  | Threaded Dispatch                       | 21 |

|      | 3.5.4  | Indirect Threaded Dispatch              | 24 |

|      | 3.5.5  | Subroutine Threaded                     | 25 |

| 3.6  | Instru | action Optimization                     | 25 |

|      | 3.6.1  | Super-instruction                       | 26 |

|      | 3.6.2  | Selective Inlining                      | 26 |

|      | 3.6.3  | Replication                             | 27 |

| 3.7  | Othe   | r Related Work                          | 28 |

|      | 3.7.1  | Instruction Reordering                  | 28 |

|      | 3.7.2  | Code Generator for Interpreter          | 28 |

| 3.8  | Mode   | ern Branch Predictor                    | 29 |

| 3.9  | Chap   | ter Summary                             | 29 |

| Chap | ter 4  | Switch-based Shadow Tree Interpreter    | 31 |

| 4.1  | Over   | view                                    | 31 |

| 4.2  | Chall  | enges in AST Interpreter                | 31 |

| 4.3  | Shad   | ow Tree Overview                        | 32 |

|      | 4.3.1  | Why Tree Structure                      | 34 |

| 4.4  | Exec   | ution Model                             | 34 |

|      | 4.4.1  | Runtime Optimization                    | 34 |

|      | 4.4.2  | Example of Pre-runtime Optimization     | 35 |

|      | 4.4.3  | Example of In-runtime Optimization      | 35 |

|      | 4.4.4  | Summary                                 | 35 |

| 4.5  | SSTI   | or Bytecode Representation              | 36 |

| 4.6  | Chap   | ter Summary                             | 37 |

| Chap | ter 5  | Implementation of Soufflé               | 38 |

| 5.1  | Over   | view                                    | 38 |

|      | 5.1.1  | Challenges and Legacy Implementation    | 38 |

|      | 5.1.1  | Chancinges and Legacy implementation    | 50 |

| -    |        | -                                       |    |

|        |       | CONTENTS                                         | vii |

|--------|-------|--------------------------------------------------|-----|

|        | 5.1.3 | Soufflé Virtual Machine                          | 43  |

|        | 5.1.4 | Data Structure Adapter                           | 45  |

| 5.2    | Chaj  | pter Summary                                     | 49  |

| Chap   | ter 6 | Experiment and Evaluation                        | 51  |

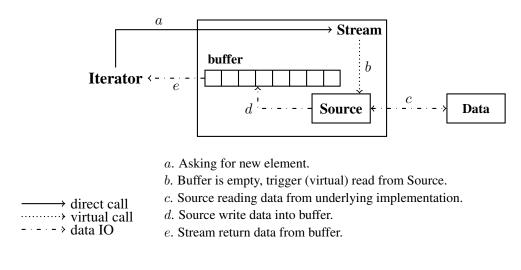

| 6.1    | Perf  | ormance Measurement on SVM and STI               | 52  |

|        | 6.1.1 | Semantic Density                                 | 53  |

|        | 6.1.2 | Summary                                          | 55  |

| 6.2    | Inve  | stigation on Indirect Threaded Code Optimization | 56  |

|        | 6.2.1 | CPython Experiment Setup                         | 57  |

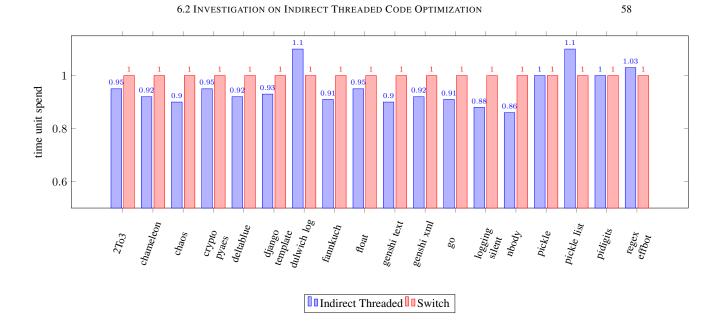

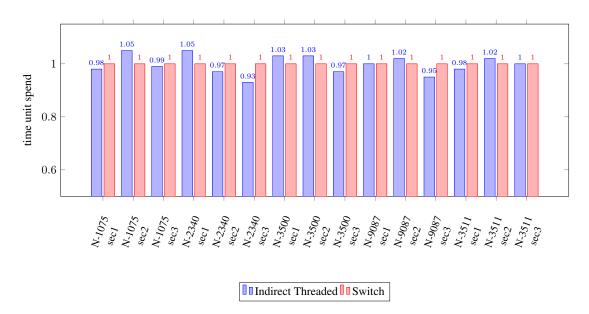

|        | 6.2.2 | CPython Experiment Result and Evaluation         | 57  |

|        | 6.2.3 | SVM Experiment Result and Evaluation             | 58  |

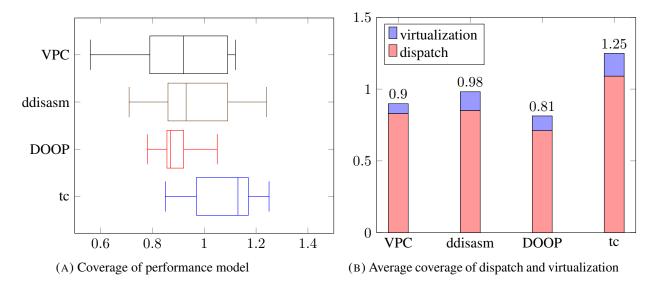

| 6.3    | Perf  | ormance Model                                    | 59  |

|        | 6.3.1 | Model Hypothesis and Definition                  | 59  |

|        | 6.3.2 | Calculate Dispatch Cost                          | 60  |

|        | 6.3.3 | Calculate Overhead in Data Structure Adapter     | 61  |

|        | 6.3.4 | Experiment Result and Evaluation                 | 61  |

| 6.4    | Supe  | er-Instruction Optimization                      | 62  |

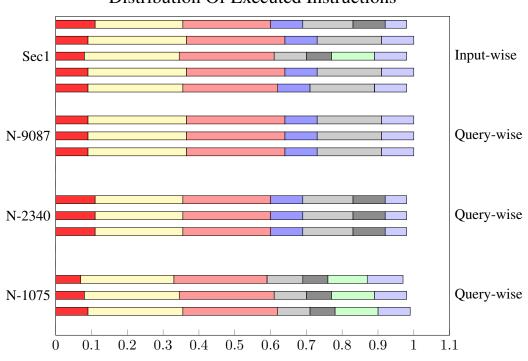

|        | 6.4.1 | Operation Distribution                           | 62  |

|        | 6.4.2 | Super-Instruction Implementation                 | 63  |

|        | 6.4.3 | Result and Evaluation                            | 65  |

| Chap   | ter 7 | Conclusion and Future Work                       | 68  |

| 7.1    | Con   | clusion                                          | 68  |

| 7.2    | Futu  | re Work                                          | 69  |

|        | 7.2.1 | Performance Model                                | 69  |

|        | 7.2.2 | Data Structure Adapter                           | 70  |

|        | 7.2.3 | Soufflé Tree Interpreter                         | 70  |

|        | 7.2.4 | Soufflé Virtual Machine                          | 71  |

| Biblio | graph | y                                                | 72  |

| .1     | Detai | ls on RAM                                        | 76  |

## **List of Figures**

| 2.1 | Soufflé execution model                                              | 8  |

|-----|----------------------------------------------------------------------|----|

| 2.2 | Illustration of two engines                                          | 8  |

| 2.3 | Ram Node                                                             | 10 |

| 2.4 | Source program                                                       | 11 |

| 2.5 | Control flow graph                                                   | 11 |

| 2.6 | Datalog program                                                      | 11 |

| 2.7 | Soufflé application example                                          | 11 |

| 3.1 | AST representation, some nodes are omitted for demonstration purpose | 14 |

| 3.2 | Example of virtual dispatch                                          | 16 |

| 3.3 | Example of stack VM instructions                                     | 17 |

| 3.4 | Example of register VM instructions                                  | 18 |

| 4.1 | Shadow tree overview                                                 | 33 |

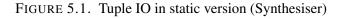

| 5.1 | Tuple IO in static version (Synthesiser)                             | 48 |

| 5.2 | Tuple IO in dynamic version (Interpreter)                            | 48 |

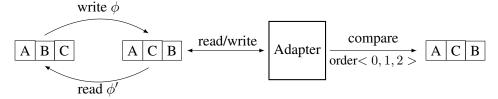

| 5.3 | Diagram of Stream and Source mechanism                               | 49 |

| 6.1 | Performance evaluation on different implementation                   | 53 |

| 6.2 | Source program                                                       | 54 |

| 6.3 | RAM representation of the main evaluation body                       | 54 |

| 6.4 | Evaluation of iterative-statement in STI                             | 55 |

| 6.5 | Evaluation of iterative-statement in SVM                             | 55 |

| 6.6 | Cpython performance using different dispatch methods                 | 58 |

| 6.7 | SVM performance using different dispatch methods                     | 58 |

|     | LIST OF FIGURES                                                                               | ix |

|-----|-----------------------------------------------------------------------------------------------|----|

| 6.8 | Performance model evaluation                                                                  | 62 |

| 6.9 | Instructions distribution input-wise and query-wise. Instructions that are executed less then |    |

| 1   | % are discarded.                                                                              | 64 |

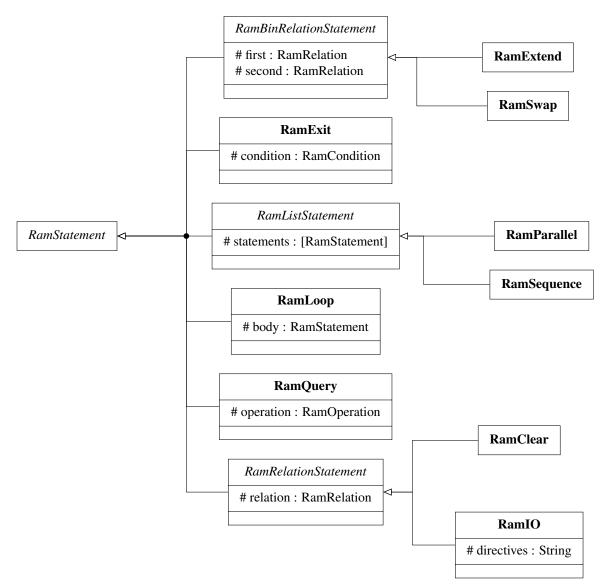

| .1  | RAM                                                                                           | 76 |

| .2  | RAM Statement                                                                                 | 77 |

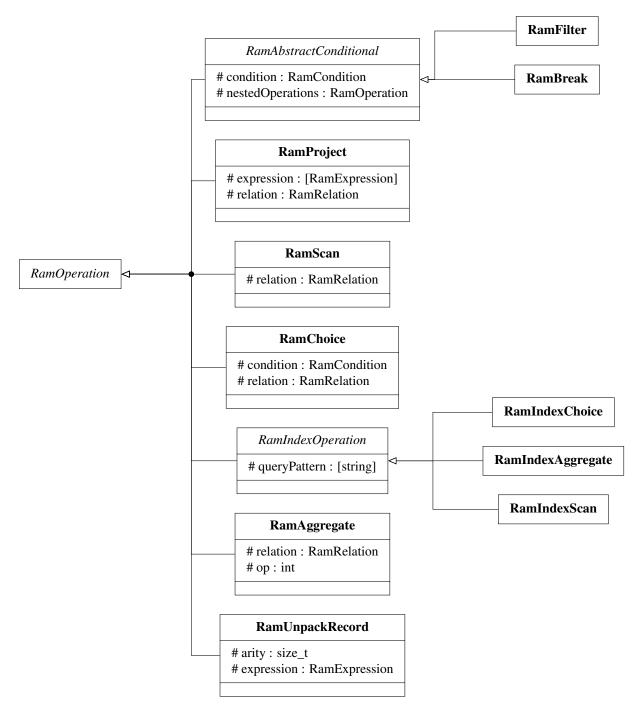

| .3  | RAM Operation                                                                                 | 79 |

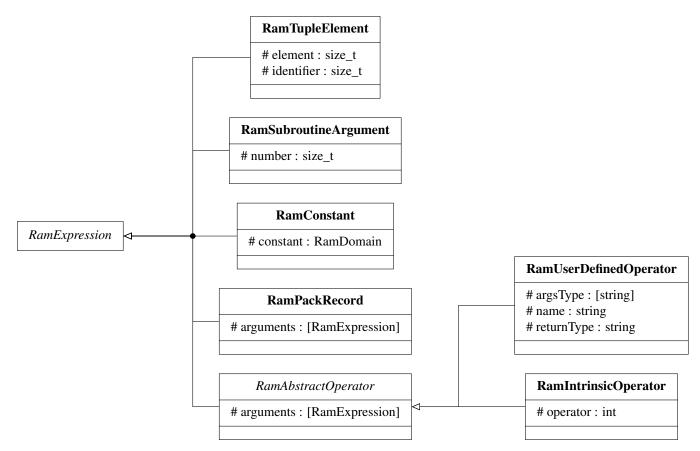

| .4  | RAM Expression                                                                                | 80 |

| .5  | RAM Condition                                                                                 | 81 |

|     |                                                                                               |    |

## List of Tables

| 3.1 | Prediction result of different dispatch methods with BTB | 23 |

|-----|----------------------------------------------------------|----|

| 3.2 | Superinstruction with switch dispatch and BTB            | 26 |

| 3.3 | Replication with BTB and threaded code                   | 27 |

| 3.4 | Replication resulting in increasing misprediciton        | 28 |

| 6.1 | Operation density                                        | 56 |

| 6.2 | Performance Result                                       | 67 |

#### CHAPTER 1

## Introduction

Soufflé (Jordan et al., 2016; Scholz et al., 2016) is a highly efficient logic engine that is used in various applications including static program analysis in Java (Antoniadis et al., 2017) and Tensor Flow programs (Sifis et al., 2020), security-oriented analysis in Ethereum Virtual Machine (Grech et al., 2019) and network analysis in Amazon Web Services (Backes et al., 2019).

Soufflé's programming language overcomes some of the limitations of classical forward chaining languages such as Datalog. For example, programmers are not restricted to finite domains, and the usage of functors and records are permitted. Soufflé obtains its high performance with its synthesiser, which compiles the source program into an equivalent, highly parallel C++ program.

However, there is an alternative mode of execution for Soufflé programs, i.e., the *Interpreter*. Unlike the compiler, which is only responsible for synthesising the source program into an equivalent and efficient form of the target language (without computing the actual result), the interpreter executes the logic program directly. In general, an interpreter breaks the execution into several steps. In the first step, a semantically equivalent, high-level, abstract intermediate representation (IR) is generated from the source program, e.g., a tree representation or a bytecode stream. The interpreter loop commences the dispatch of instructions, i.e., the interpreter is invoked, it decodes the IR one by one and executes the virtual instruction. The interpreter loop terminates when the logic program has completed the calculations. A common implementation of an interpreter is to directly execute the input program on its Abstract Syntax Tree (AST) generated by the scanner/parser.

Although the performance of an interpreter is sub-optimal compared to a highly-optimised compiled binary, it still has several advantages. Firstly, the interpreter has no compile-time costs, and can execute an input program immediately after parsing. In contrast, a compiler spends a considerable amount of time for synthesising; for example, the compilation of a Soufflé program can be substantial, exceeding multiple minutes. Secondly, being able to execute the program right away is extremely helpful in an

#### **1** INTRODUCTION

active project development cycle since users can obtain feedback right away instead of recompiling the source program every time when they make a change. Thirdly, no host language compiler is required for executing the input program. Once the interpreter executable is deployed on the host machine, there are no further dependencies for executing the input programs. This sometimes makes the interpreter the only option for a sophisticated system environment. For example, Amazon Web Service Lambda does not have a C++ environment; hence deploying the interpreter as an executable is the only option to have Soufflé engine running in such a cloud environment. Fourthly, interpreters are more portable and less labour-intensive to be implemented.

There has been continuous research in the implementation of efficient interpreters (Ertl and Gregg, 2001, 2003) mainly targeting imperative and object-oriented languages, but this research field has been relatively inactive in the last decade. As a consequence, most of the experiments and conclusions from this line of research is no longer valid or at least need to be revisited as modern hardware has evolved. For example, the improvement in branch-predictions units, pipelines, and cache architectures have made a significant effect on the interpreter's performance (Rohou et al., 2015).

Soufflé's logic engine also has a different style of instructions than traditional interpreters and virtual machines such as Python and Java bytecode. Soufflé's instructions set are relational algebra instructions, which can be very heavy-weight performing relational algebra operations on large tables in contrast to light-weight and small inexpensive computations in an imperative language. In addition to that, Soufflé's excellent performance depends highly on its parallel, efficient data structure which is specialised for logic evaluation (Jordan et al., 2019b, 2020). However, the data structures are statically typed classes (written in C++ ) and have been designed for the synthesiser. These data structures cannot be directly accessed by the interpreter during runtime due to the lack of a common interface for them. As a result, the design of Soufflé's interpreter must overcome this issue and utilise the statically typed data structure for better performance. In summary, there are different design decisions to be made, and the trade-offs differ from traditional computational engines.

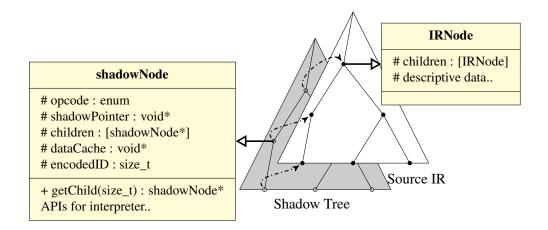

In this work, we explore the design space by introducing a new tree interpretation strategy - Switch-based Shadow Tree Interpreter (SSTI). The new strategy evolved from the AST interpreter and introduces a new executable IR - the *Shadow Tree*. The shadow tree is a light-weight tree structure that takes the shape of the source IR as a tree (hence the name, shadow) and enables runtime optimisation with improved efficiency and maintainability by separating descriptive format of an AST from the execution state of an interpreter. The standard approach implementing an interpreter on AST is the use of a

#### **1** INTRODUCTION

visitor pattern (Gamma et al., 1994). However, using the visitor pattern causes performance issue due to the double-dispatch (i.e. two virtual calls in two class hierarchies). In addition, it implies software engineering challenges because execution state of the interpreter quite often requires modifications of the AST changing the nature of this data-structure from a descriptive format to an executable one. Our SSTI aims to solve both the performance and engineering issues.

In this work, we adapt and evolve the state-of-the-art interpreter techniques for modern CPUs and applying them in the context of Soufflé. We implement two variants of high-performance interpreters for Soufflé. Those interpreters pursue different strategies executing Soufflé programs. The first interpreter is a stack-based virtual machine interpreter whereas the second interpreter utilise the SSTI strategy.

Soufflé's Stack-based Virtual machine (SVM) commits to a linear execution order model, where programs are represented as a stream of instructions. The program computation is advanced by incrementing a virtual instruction pointer (vPC) and by conditional/unconditional goto-statements. The SVM instruction set is fine-grained, it uses small, light-weight instructions for operations, such as stack pushing/poping to pass intermediate results during computation, and a virtual jump operation to transfer control to an alternative branch.

Soufflé's Tree interpreter (STI) utilise the Switch-based Shadow Tree strategy. It applies better engineering principle compared to traditional AST interpreter and provides runtime optimisation easily by separating descriptive information from executable state. In addition to that, STI is a recursive tree interpreter where the control flow follows a recursive tree traversal pattern based on the program semantic. In contrast to SVM, the semantics of STI is more abstract, high-level and follows directly from the relational algebra machine. Instead of fully emulating the program control flow in a low-level style by utilising vPC and virtual goto statement. For example, an iterative statement is emulated directly by a dedicated tree node whereas the SVM would issue several instructions for building a loop.

Both implementations have been highly-tuned for the execution of logic programs. We show that the STI can outperform SVM in our current implementation by 7 - 15% due to its high semantic density that fits better in the relational algebra instructions. In addition to that, the tree traversal pattern in STI, which relies on light-weight tree nodes and switch dispatch, overcomes the performance overheads of the double-dispatch in the visitor pattern, and still provides great flexibility for change in the future. We conduct experiments to highlight the performance impact of these strategies.

## **1.1 Contributions**

We summarize the contributions of this work as follows,

- (1) We design and implement a stack-based Virtual Machine interpreter for Soufflé. We analyse its performance and revisit its instruction set design to hand-tailor it for a logic programming language like Soufflé. We conclude that a fine-grained instruction set may not fit well in Soufflé due to its low semantic density, which results in 10% - 36% of more dispatches compared to STI in the context of relational algebra operations.

- (2) We design a new tree interpreter implementation strategy, which applies sound engineering principle. The new strategy provides great flexibility for runtime optimisations. We implement Soufflé's default interpreter based on this strategy. We conclude that a tree-walk interpreter is not necessary slower compared to Virtual Machine interpreter. In particular, the coarse-grained instruction set in STI fits well in the context of logic programming, making it 7% 15% faster than the SVM implementation. We have deployed this interpreter into the main branch of Soufflé since it has excellent performance, and it is easy to maintain and extend, which are essential properties for Soufflé as a rapid development environment.

- (3) We review optimisation techniques for interpreters, and identify the common bottleneck of interpreter performance, which is the dispatch costs. We analyze the technique not only for its impact on performance but also its implementation difficulty and maintainability. We also implement two of the techniques, namely indirect threaded code, and super-instructions (Ertl and Gregg, 2003) in Soufflé and observe their impact. We conclude that indirect threaded code is still effective in an imperative language like CPython but is sub-optimal in Soufflé. On the other hand, super-instructions, if applied carefully with support of statistics data, can result in a good performance gain.

- (4) We build a performance model for STI. This model aims to provide us with a better understanding of the performance difference between interpreter and compiler. We are able to capture most of the performance gap in relatively simple benchmarks to identify the current bottlenecks (i.e.,the dispatch costs and virtualisation layer of the data structure).

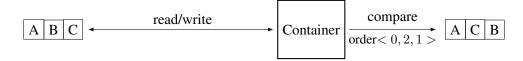

- (5) We build a dynamically typed adaptor classes for the statically typed data structures in Soufflé so that the interpreter can uniformly access the data. To amortize the virtualization costs of the adaptors, we design iterators with buffers and other implementation efforts to overcome the performance penalties of the adaptor.

#### 1.1.1 Outline

The thesis is organised as follows:

In Chapter 2 we give an overview of the Soufflé language, including an introduction to Soufflé's architecture and its intermediate representation, namely the Relational Algebra Machine (RAM). In Chapter 3, we give some background about related work in interpreters, including different architectures, performance results and optimization techniques. In Chapter 4, we give the Switch-based Shadow Tree technique, we present its implementation detail and we argue about its advantages in a language like Soufflé. In Chapter 5, we give implementation detail about SVM and STI. In Chapter 6, we present out experimential results and evaluations. In Chapter 7, we conclude the work and provide potential avenues for future work. Chapter 2

## Soufflé

## 2.1 Logic Programming

Soufflé is a variant of Datalog (Abiteboul et al., 1995), which is a fragment of first-order logic with recursion and started as a Database query language. Instead of focusing on *how* to solve a problem, Datalog programmers express *what* to solve in the form of *Horn Clauses*. Horn clauses can either be facts, rules or goals. Although Datalog commenced as a Database query language, it evolved and overcame the initial restrictions such as finite domains. Its applications can be found in many fields, including program analysis (Jordan et al., 2016), Big Data (Shkapsky et al., 2016), security analysis (Whaley et al., 2005) and network analysis (Seo et al., 2013), etc.

#### 2.1.1 Basic Structure of Logic Programs

Logic programs consists of Horn clauses of the form:

$$L_0:-L_1,...,L_n$$

where each  $L_i$  has the form  $p_i(x_0, ..., x_m)$  for some value m; we say  $L_i$  is a *literal* with *predicts*  $p_i$  of size m, and each  $x_i$  can either be a *constant* or a *variable*. The left hand side of the clause  $(L_0)$  is referred as *head*, while the right hand side of the clause  $(L_1, ...)$  is referred to as the *body*. When the body of the clause is empty, it represents a *fact*; if the head is empty, it represents a goal; otherwise, the clause represents a *rule*.

Facts are also known as an Extensional Database (EDB) in Datalog, and are unconditional true. In a forward-chaining language such as Datalog, facts are usually used as the starting point of the computation:

In the example above, the facts mean Bob is the parent of Alice and Alice is the parent of Carol.

The body of the rule consists of a set of conjunctive predicates. A rule can be interpreted as follows: If all the predicates in the body hold, then the head holds as well. The derived facts are called Intensional Database (IDB). These facts are the computation results of some other EDB and IDB.

$$grand\_parent(X, Z) := parent(X, Y), parent(Y, Z).$$

In the example above, the rule means that X is Z's grandparent if X is the parent of Y, and Y is the parent of Z.

A question mark and a dash followed by a single literal forms a goal, ?:-L. Goals are queries to the Database, given the rule and facts in the above paragraph and with the query:

$$?:=grand\_parent(X,Y).$$

Datalog answers all the grandparent relations in the Database - Bob is the grandparent of Carol.

In addition to that, it is also possible to have recursive rules and negation in Datalog (Abiteboul et al., 1995). Although the theory behind them can be complicated and beyond the scope of this introduction, their semantic are intuitive and should be straightforward to the reader now.

## 2.2 Overview of Soufflé

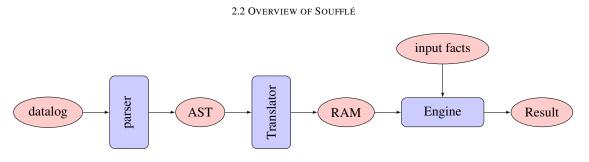

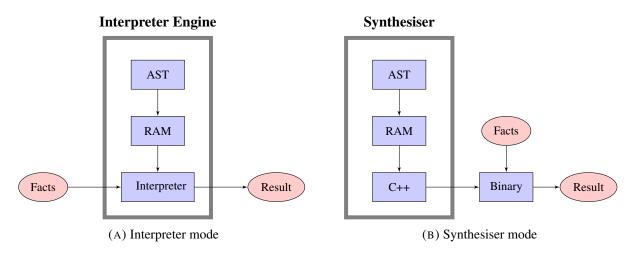

A logic engine like Soufflé breaks up the execution of logic programs into phases as shown in Figure 2.1. In the first phase, Soufflé takes a Datalog program as input and generates an abstract syntax tree (AST). In this stage, the input is checked for syntax and semantic errors first. After the semantic checks, a sequence of high-level optimisations is applied. In a subsequent stage, the AST IR is translated to a

FIGURE 2.1. Soufflé execution model

Relational Algebra Machine (RAM) program, which is an imperative description of the program in the form of relational algebra queries and control flow.

In the last stage, the RAM program is either synthesised to a C++ program (Figure 2.2b), or interpreted using an interpreter as shown in Figure 2.2a.

FIGURE 2.2. Illustration of two engines

#### 2.2.1 The RAM Language

Soufflè eventually translates the AST into the Relational Algebra Machine representation, which is a tree representation of the source Datalog program. RAM is designed specifically for executing relational algebra operations by an imperative programming style. The design of RAM also supports native parallel statements where a sequence of RAM statements can be executed in parallel until all the sub-statements are completed (Scholz et al., 2016). Furthermore, the static nature of RAM semantic ensures efficient pre-runtime optimisation, such as computing the index for fast range query and load-balancing in parallel computation (Subotić et al., 2018).

#### 2.2 OVERVIEW OF SOUFFLÉ

In detail, RAM is represented as a tree-structure in the program memory and used as a description for executing logic programs that were already lowered to an imperative form with relational algebra operations. A RAM program is consists of of relations, subroutines and the main program, where the main program is the root of the RAM tree. In the remaining part of this section, we give some typical examples of RAM language, with their semantic explanations.

RAMStatement specifies a series of actions that should be executed by RAM. Typical examples of statements in RAM are: Sequence, which is a compound statement consisting of a list of other statements that should be executed in order. Sequence also has a parallel version Parallel, where the child statements can be executed in parallel. In addition, Clear statement specify the action of clearing the content of a target relation; Swap statement is the action of swapping the content of two relations. Finally, Loop statement represents a forever loop, it is used to compute a fixed-point evaluation, along with Exit statement - forever computation is terminated once the exit condition is met.

RAMExpression defines the expressions in RAM. A Number expression returns a constant number whereas TupleElement accesses and returns element from a tuple access in a relation during computation. In addition to that, Soufflé enables record to support abstract user-defined compound type; a PackRecord is used to evaluates and store a user-define record.

RamCondition defines control flow operations in RAM. Conjunction defines a conjunction of conditions, evaluated to true if all the conditions are true; Negation simply negates the result of another *RamCondition*; EmptinessCheck and ExistenceCheck are used to check if target relation is empty, or if a tuple exists in the target relation. Finally, Constraint represents a binary constraint operation, such as less-equal.

The centre of the execution is the Query statement, representing a loop-nest of operations, which are defined by *RamOperation*. Clauses evaluation is translated into a series of nested loops in RAM. For example, consider the rule:

$a = b \cap c$

To derive a, RAM translates the rule into following loop-nested operations (unoptimised):

for

$$(x \in b)$$

for  $(y \in c)$

if  $(x == y)$

project x into a

In particular, typical loop-nested operations are: Scan operation iterates through all the tuples in a relation; Choice operation is similar to Scan, but stops once some condition holds; Project operation inserts a tuple into the target relation. Many loop-nested operations also have a index version to support efficient query; for example, ScanIndex iterates through only the tuples in the relation that follows a particular range pattern.

The base class of RAM nodes is RamNode and auxiliary operations are defined in order to support operations on RAM node more easily (Figure 2.3). For example, a visitor pattern is built to enables different execution models on the RAM, such as synthesising, optimisation, etc. A clone method is defined for cloning a source node; a rewrite function is built for modifying the source node and a print function is used for debugging and logging purpose. Finally, getChildren returns the children of the node and apply function would apply the given mapper to all the nodes.

In the following section, we provide an example resembling a security analysis and its RAM representation. We refer the reader to Appendices .1 for a detailed description about RAM semantic.

| RamNode                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>+ getChildren() : [RamNode*]<br/>+ clone() : RamNode*<br/>+ rewrite(RamNode*, unique_ptr<ramnode>) : void<br/>+ apply(RamNodeMapper&amp;) : void</ramnode></pre> |

| <pre># print(ostream&amp;) : void # vector<ramnode*></ramnode*></pre>                                                                                                 |

FIGURE 2.3. Ram Node

#### 2.2.2 Example

Figure 2.7 illustrates a simple security analysis application in Soufflé. The logic code identifies potentially vulnerable region in a program and will report them. On the first glance of the source code in Figure 2.4, the region may be protected because the program might execute the protect statement on

FIGURE 2.7. Soufflé application example

line 5 before reaching the vulnerable zone. However, the control flow graph (Figure 2.5) suggests that the critical region is still accessible under an unprotected state in case of a zero-trip loop, and makes the program vulnerable; this happens when the initial condition of the while loop is not met. Although a programmer may not easily detect the security failure, it can be picked up by the Datalog program immediately.

Listing 1 shows fragments of the RAM representation of the example. The RAM representation describes the logic program in an imperative/relational format. Starting from line 1 to 3, it projects the initial data into its corresponding relations. The next step is to generate the knowledge for *Unsafe* relation, which corresponds to the logic rule of *Unsafe* in the Datalog program (Figure 2.6). In the RAM representation, a LOOP statement will be evaluated until the EXIT condition at line 9 is met (until a fixed-point is reached). Within the LOOP statement, there are two nested for-loops (Scan) that iterate through all the tuples in *Unsafe* and *Edge* relations and try to generate new knowledge about *Unsafe* based on the rule. Then, any newly generated knowledge will be inserted into *Unsafe* at line 11 - 12; RAM will keep executing the loop until no new knowledge is generated in a whole iteration. Finally, after the computation is completed, the RAM program iterates though the *Vulnerable* relation, checking if any of the tuples also exist in *Unsafe*. This corresponds to the logic rule of *violation* in the Datalog program: a statement will trigger a violation if it is a vulnerable statement and can be reached under an unsafe state. The last statement simply outputs all the knowledge about *Violation*. 2.3 CHAPTER SUMMARY

Listing 1 RAM representation of the example Datalog

```

PROJECT ("while") INTO delta Unsafe

1

PROJECT ("while", "protected") INTO Edge

2

PROJECT ("vulnerable") INTO Vulnerable

3

4

. . .

5

LOOP

6

QUERY

7

IF ((NOT (delta_Unsafe = \emptyset)) AND (NOT (Edge = \emptyset)))

8

9

FOR a IN delta_Unsafe

FOR b IN Edge ON INDEX a.0 = b.0

10

IF ((NOT (b.1) ∈ Unsafe) AND (NOT (b.1) ∈ Protect))

11

PROJECT (b.1) INTO @new_Unsafe

12

EXIT (new_Unsafe = \emptyset)

13

QUERY

14

FOR a IN new_Unsafe

15

PROJECT (a.0) INTO Unsafe

16

17

SWAP (delta_Unsafe, new_Unsafe)

CLEAR new_Unsafe

18

END LOOP

19

20

IF ((NOT (Vulnerable = \emptyset)) AND (NOT (Unsafe = \emptyset)))

21

FOR a IN Vulnerable

22

IF (a.0) \in Unsafe

23

PROJECT (a.0) INTO Violation

24

25

OUTPUT Violation

26

```

## 2.3 Chapter Summary

In this chapter we introduce Soufflé execution model and its underlying representation - Relational Algebra Machine. The purpose of this chapter is to give the reader a brief idea about Soufflé as a logic engine and how its semantic and execution model differs from traditional imperative language. Those characteristics eventually play an essential role in the design of the interpreter implementation, as well as the performance. In the next chapter, we present the related work and overview in the research areas of interpreter implementation.

#### CHAPTER 3

## **Background and Related Work: Interpreter and Dispatch**

## 3.1 Overview

In this chapter, we give a detailed survey about previous work that is related to this project. To implement an efficient interpreter, it is necessary to investigate existing interpreter architectures, such as AST interpreters and the bytecode interpreters. More importantly, we would like to understand the virtual dispatch as the performance bottleneck in the interpreter - what is a virtual dispatch, and why is it slowing down the interpreter performance? Finally, we investigate the optimisation techniques that target on the interpreter architecture, instruction set design and dispatch process.

## 3.2 Interpreter

Interpreters are a popular technique when implementing a programming language. Compared to compilers, interpreters are easy to implement, have excellent portability and can provide active feedback in program development. However, interpreters usually run much slower than compilers (Wiedmann, 1983), so extra care must be taken regarding performance issue. While a lack-of-optimisation interpreter can be slower by a factor of 1000 than compilers, an efficient and well-optimised interpreter can be slower only by a factor of 10 (Ertl and Gregg, 2003).

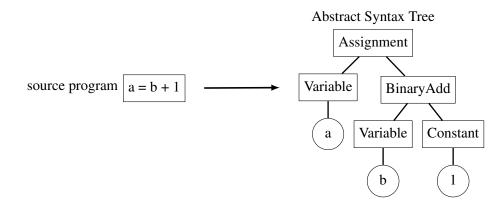

An interpreter usually executes on an intermediate representation, either an Abstract Syntax Tree (AST) or a bytecode representation. The AST interpreter and bytecode interpreter differ from their implementation difficulty, semantic and performance. In the following sections, we will discuss interpreter implementations.

FIGURE 3.1. AST representation, some nodes are omitted for demonstration purpose

## **3.3 Abstract Syntax Tree Interpreter**

Abstract Syntax Tree (AST) is a tree structure representation of the source program. An interpreter that directly executes on the AST representation is called an *AST interpreter*, and implementing an AST interpreter is straightforward (Aho et al., 2006; Gabbrielli and Martini, 2010). First, no effort is needed for the interpreter instruction set design as its semantics is given by AST. Second, the AST representation is 'free' because it is usually the output of a canonical language implementation, such as parser and semantic checker; Figure 3.1 gives an example of the AST generated by a parser. Finally, the software engineering technique related to AST interpreters is very mature using object-oriented language features. For example, the instruction dispatch can be done with the help of virtual function calls and the visitor pattern (Gamma et al., 1994). With this technique, an interpreter engineer will be able to produce a concise and maintainable interpreter quickly.

However, the recursive nature of an AST representation is usually considered to be unwieldy for interpreters. The tree visiting involves the recursive calls causing overheads on the program stack and runtime. In addition to that, as pointers connect tree nodes in computer memory, some would also argue that traversing AST is not cache-friendly (Ladner et al., 1999).

In the following sections, we briefly introduce two conventional approaches when implementing an AST interpreter: virtual function dispatch, which usually found on modern object-oriented languages like C++ and Java; and switch dispatch which uses tagged node and switch statement.

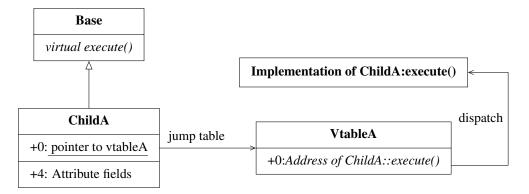

#### 3.3.1 Virtual Function and Visitor Pattern

Building an AST interpreter using virtual methods is common in a language that supports polymorphic types. All tree nodes inherit from a base node type with an 'execute' interface and have its own implementations for that interface. The program is then executed by calling the 'execute' function on the root of the tree. This approach relies on the virtual dispatch of the host language: in C++ the dispatch is done by looking up through a virtual function (Bacon and Sweeney, 1996) table (vTable) in the assembly code as shown in Figure 3.2. The vTable is generated by the compiler and is hidden under the hood from the programmer. However, this also means that the programmer has no control over the dispatch mechanism. This can be a disadvantage since the execute method will be invoked frequently. Another problem wiht such a simple approach is that the interpreter's state may be deposited in the AST and the AST require the additional execute method. As a consequence, the AST becomes polluted. This is not ideal, because many other parts of the language implementation will use the AST.

To overcome the engineering issues of a simple virtual execute method in AST, a visitor design pattern was proposed as an improved strategy for implementing an interpreter. The visitor pattern is a behavioural design pattern that provides different operation implementations on a data structure without introducing new operations inside the data structure.

A visitor pattern for implementing an AST interpreter is desired as AST is usually shared among other parts of the language implementation; such as optimiser and semantic checker, hence different algorithm/implementation are needed to operate on the AST. This can be done by providing each child node with a virtual 'accept' function that takes a visitor; the visitor then chooses the appropriate 'execution' depends on the given tree node. However, the issue is that the visitor pattern introduces a double-dispatch routine: one in the 'accept' function and one in the 'execution' function, therefore, doubling the cost of dispatching during runtime.

#### 3.3.2 Switch Dispatch

When implementing an AST interpreter in a language that does not support polymorphic type, one can always use a tag in a node and a switch statement to emulate a virtual dispatch in an object-oriented language. A tag can be expressed as an Enum variable indicating the associated AST type; a dispatch can then be performed by using a switch statement on the tag. Under the hood, the switch statement can be either lowered into a binary search or linear search on the tagged nodes, or a jump table (Berndl

FIGURE 3.2. Example of virtual dispatch

et al., 2005; Korobeynikov, 2007). Compared to the virtual dispatch, switch dispatch does not involves function call, hence no overhead on the program stack.

In addition to that, there are multiple dispatch optimisations that can be applied on to the switch dispatch, such as Threaded Code and Selective Inlining. This makes switch dispatch a very flexible choice when implementing an interpreter. The related optimisation techniques will be discussed later in this Chapter.

## 3.4 Virtual Machine Interpreter

Modern computers can be complicated to manage due to their complexity. Virtual machine technology as a solution for that has been used in many fields including software development, operating system and language implementation. A virtual machine provides an interface between the hardware architecture and users, bringing flexibility and usability (Smith and Nair, 2005).

A system-level virtual machine provides the user with a completed virtualized hardware environment: they aim to emulate a physical machine. On the contrast, a process-level virtual machine is designed for a particular software, their functionality is limited, but they can be implemented in an easier manner.

A high-level language (HLL) virtual machine, as a subtype of the process-level virtual machine, is specially designed for language development. In HLL VM, the virtualization layer sits between the operating system and guest language by providing a bytecode intermediate representation, which is usually semantically close to assembly language but with a higher abstraction level. With a unified IR across different platforms, the software can be executed as long as the program can be compiled into such representation. The fundamental core of an HLL VM is usually an interpreter which directly execute

the code stream by a fetch-dispatch-execute loop. More performance-concern VMs would consider applying techniques such as JIT to execute the program on the host platform directly.

In contrast to AST, bytecode representation is a sequential representation; the computation is advanced by the control of vPC and branch statements (Torczon and Cooper, 2007). The nature of a bytecode representation is usually low-level and semantically close to assembly language. In addition to that, when designing an HLL VM, one has to decide what architecture of the virtual environment to use, either a stack-based VM or a register-based VM. The choice of the underlying architecture will not only affect how the instruction set will be designed but also the potential performance and memory consumption.

In the following sections, we briefly introduce two architectures and then discuss their difference.

#### 3.4.1 Stack-based VM

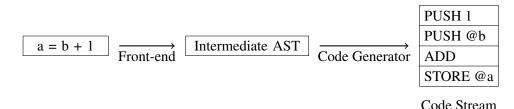

A stack-based VM uses a virtual stack to pass intermediate result during the computation (Schoeberl, 2005). The virtual stack is usually implemented by a dynamic sized, sequential data structure, such as a list; the arguments and the intermediate results of the computation are passed between different operations though push and pop operation in a last in first out (LIFO) manner. As an example for stack-based VM and its instruction set, figure 3.3 demonstrate the code stream generated to perform a simple assignment operation, a = b + 1. A well-known example of stack-based VM is the Java Virtual Machine (Tim et al., 2020), which compile the source language into JVM bytecode representation and can be later executed by the interpreter.

FIGURE 3.3. Example of stack VM instructions

#### 3.4.2 Register-based VM

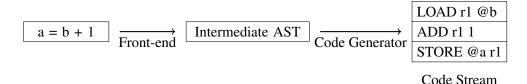

A register-based VM uses a sequential data structure with random accessibility to emulate the hardware machine registers; unlike real word hardware, register-based VM often has no limitation on the number

virtual registers - it can have as many as it needs (Scott, 2009). The data in register-based VM is passed between operation via 'move' and 'load' instructions, in contrast to stack-based VM, which can only access the top of the virtual program stack, there is no restriction on how/when the data can be accessed in register-based VM. The code stream generated to perform the example assignment is shown in Figure 3.4. A typical example of a register-based VM is the Dalvik Virtual Machine. In Dalvik VM, common operations usually reference up to 16 registers, in some rare case, some operation can reference up to 65535 registers (Ehringer, 2010).

FIGURE 3.4. Example of register VM instructions

#### 3.4.3 Stack-based VM versus Register-based VM

A big question in the design of VMs is whether a stack-based VM or a register-based VM is more efficient.

As we can see in the above examples, it requires more instructions for stack-based VM to perform the same operation as register-based. This is because stack-based memory access is implicit to the top of the stack while register-based memory access can be explicit to any register. Therefore, register-based VM can be more efficient when moving around the intermediate result during computation. However, in register-based VM, memory-related instructions tend to have larger sizes per opcode since they require extra space for arguments to specify the target registers. The difference in the size of the instruction set and opcode size plays a vital role regarding the performance.

Winterbottom et al. (Winterbottom and Pike, 1997) in their study found that compiling the source code to a register-based representation can result in efficient gain compared to a stack-based representation in Dis. Later Gregg et al. (Gregg et al., 2005) gave a more detailed experiment and quantitative data by translating a stack-based JVM to an equivalent register-based JVM. They found that the resulting register-based code reduces the total number of VM instructions by 34.88% while increasing the size of the code by 44.81%. As to extend Davis et al.'s study, Shi et al. (Shi et al., 2008) offered a more aggressive and efficient algorithm that can translate two representations between each other. They give a comprehensive tutorial on how to do the translation using copy propagation and how to eliminate

#### 3.5 DISPATCH TECHNIQUES

duplicate instruction. Their experiment on JVM indicates that register-based spend 26.5% - 32.3% less time to execute the same program, with the drawback of having 25% larger bytecode size.

Despite the potential performance disadvantage, the stack-based VM still has the advantage of being easy to implement. Building an IR generator and interpreter engine based on stack-based instruction set can be very straightforward; unlike the register-based VM, which often require the input IR to be given in Static Single Assignment (SSA) form and need register allocation algorithm to help provide efficient data allocation and fetching.

To sum up, the register-based VM has a higher performance potential than stack-based VM due to its higher semantic density and the ability to access any register during runtime randomly; the performance boost comes with the cost of larger opcode size and greater implementation difficulty.

## 3.5 Dispatch Techniques

In the interpreter, an operation dispatch is a process of reading the next operation in the code stream and transferring control into corresponding virtual instruction for computation.

In this section, we first introduce the challenge in the interpreter dispatch process, then we examine some widely used dispatch techniques, and we discuss their characteristic in respect to their portability and efficiency.

#### 3.5.1 Branch Prediction and Context Problem

In modern computer architecture, instruction pipelining overlap multiple instructions and execute them in parallel (Bryant and O'Hallaron, 2015). This requires the CPU to foresee the actions that will be executed in future in order to schedule the pipeline. When encounter a conditional branch, it is hard for the pipeline to schedule execution since the future operations depend on runtime result. Therefore, the branch predictor is invented as a technique to help the CPU to predict the next branch location in order to schedule the pipeline successfully. In case of a misprediction, the pipeline has to flush its content and performs a reschedule, causes a pipeline stall. In an interpreter architecture, the virtual instruction to execute depends on the code stream, whereas the code stream is generated from the source program and is only known during runtime, hence each opcode dispatch is a conditional branch in the CPU.

#### 3.5 DISPATCH TECHNIQUES

In 2001, Ertl and Gregg first identified that the branch misprediction as a critical performance bottleneck (Ertl and Gregg, 2001), due to highly misprediction rate during the dispatch process, which results in severe pipeline stall. They found that a bytecode interpreter usually spends 13% of the instructions on indirect branches, much higher than a regular application. Meanwhile, they also examined many available branch predictors, including profile-guided predictor, branch target buffer (BTB), BTB2 and 2-level predictors. They found none of them suited well for an application like an interpreter, where indirect jumps are very often and involve with many possible targets.

For example, the most widely used branch predictor at the time was the BTB, which contains one prediction entry for each branch location and predict the branch target by using the last jumped location. For example, for an if-statement with two possible branches, a consequence branch (if) is used when the condition holds, and an alternative branch (else) is used otherwise; if the last evaluation result leads the program to an alternative branch, then the next prediction made on the same if-statement will simply be the alternative branch again. This naive approach results in a severe misprediction rate in a program like an interpreter - imagine all operations are dispatched from a single branch location, unless two consecutive opcodes are the same, the BTB will always mispredict. Later, this particular challenge in interpreter application is named as the 'context problem' (Berndl et al., 2005)

With the discovery of the context problem, many optimizations were invented to overcome the issue. These techniques can be categorized into two kinds, one that mainly focusing on the dispatch itself and the other focus on the virtual instruction set design. We introduce some most well-known techniques in the following section.

#### 3.5.2 Central Dispatch

Central dispatch, also known as switch dispatch if found in a standard imperative language using a switch statement, is the most natural way of writing a dispatch engine for an interpreter. The key characteristic is having a single dispatch point for dispatching all the opcode: once the computation in the virtual instruction is done, the control is given back to the central dispatcher for the next operation.

As shown in Listing 2, the dispatch point is the switch statement: it transfers program into corresponding case statement based on the opcode; after the computation, the control will go back to the top of the loop and enter the dispatch point again.

Listing 2 Example code for switch dispatch

```

#define DISPATCH() ip++; break

while (true) {

switch(code[ip]) {

case (ADD) : {

// Computation goes here

DISPATCH();

}

case (SUB) : {

// Computation goes here

DISPATCH();

}

}

}

```

Consider its underlying implementation in C when targeting at x86-64 using gcc 9.2, as shown in Listing 3. The dispatch is done by utilizing an address table (.L4) and performs the dispatch by calculating the offset of the target address in the address table (line 4 - 5). Then, the indirect jump happens at line 6. Once the virtual instruction is done, control flow is transfer into to .L2 and then returns to .L9 and ready for the next dispatch

Switch statement is available on most of the imperative language, and one can usually find an equivalent statement in other language paradigms. As long as the dispatch is always done at a single point, it can be classified as a central dispatch.

#### 3.5.3 Threaded Dispatch

Unlike central dispatch, threaded dispatch provides a dispatch point at the end of each virtual instruction; there is no need to transfer control back to a central point, each virtual instruction can handle the dispatch by themselves.

Threaded dispatch is first described by James R. Bell (Bell, 1973) as an optimization technique to improve dispatch efficiency; it requires fewer instructions to finish a dispatch process since it does not need to transfer control back to a central dispatch point.

|          | Listing 3 Underlying mechanism of switch statement in C |        |                                            |  |  |

|----------|---------------------------------------------------------|--------|--------------------------------------------|--|--|

| 1        | .L9:                                                    |        |                                            |  |  |

| 2        |                                                         | cmp    | DWORD PTR [rbp-4], 4                       |  |  |

| 3        |                                                         | ja     | .L9                                        |  |  |

| 4        |                                                         | mov    | eax, DWORD PTR [rbp-4]                     |  |  |

| 5        |                                                         | mov    | rax, QWORD PTR .L4[0 <mark>+</mark> rax*8] |  |  |

| 6        |                                                         | jmp    | rax                                        |  |  |

| 7        | .L4:                                                    |        |                                            |  |  |

| 8        |                                                         | .quad  | .L8                                        |  |  |

| 9        |                                                         | .quad  | .L7                                        |  |  |

| 10       |                                                         | .quad  | .L6                                        |  |  |

| 11       |                                                         | .quad  | .L5                                        |  |  |

| 12       | _                                                       | .quad  | .L3                                        |  |  |

| 13       | .L8:                                                    |        |                                            |  |  |

| 14       |                                                         | call   | A ( )                                      |  |  |

| 15       |                                                         | jmp    | .L2                                        |  |  |

| 16       | .L7:                                                    |        |                                            |  |  |

| 17       |                                                         | call   | B()                                        |  |  |

| 18       | тС                                                      | jmp    | .L2                                        |  |  |

| 19       | .L6:                                                    | aa 1 1 | $C(\lambda)$                               |  |  |

| 20       |                                                         | call   | C()<br>.L2                                 |  |  |

| 21<br>22 | .L5:                                                    | jmp    | • 112                                      |  |  |

| 22       | •ЦЈ•                                                    | call   | D()                                        |  |  |

| 23<br>24 |                                                         | jmp    | .L2                                        |  |  |

| 24<br>25 | .L3:                                                    | Jup    | • 12                                       |  |  |

| 23<br>26 | • 110 •                                                 | call   | D ()                                       |  |  |

| 20       |                                                         | nop    |                                            |  |  |

| 28       | .L2:                                                    | 11012  |                                            |  |  |

| 29       |                                                         | jmp    | .L9                                        |  |  |

|          |                                                         | 7      |                                            |  |  |

With the introduction of the instruction pipeline, the fewer instructions achieved in threaded dispatch became less critical to the performance. Nevertheless, later it was found to be beneficial to the indirect branch prediction in the processor (Ertl and David, 2003). At the time, the most widely used branch predictor is the branch target buffer (BTB), which uses a single buffer for each branch location and naively predict the next jump location to be the previous target of that branch location.

The central dispatch, having only a single branch location, becomes inferior here. The prediction made by BTB in central dispatch is only correct when two consecutive operations are identical in the program, which rarely happens. On the other hand, by having an individual branch location at the end of each virtual instruction, the accuracy rate of BTB can be significantly improved. Table 3.1 illustrates an example; the first column is the code stream, the prediction made by BTB before dispatching to the corresponding opcode is on the same row. The BTB in a switch dispatch fails to predict any of the

#### Listing 4 Example code for threaded dispatch

```

#define DISPATCH() goto **codeStream[ip++]

```

// codeStream = [&&ADD, ... ];

DISPATCH();

# ADD: // Computation goes here DISPATCH();

SUB:

// Computation goes here

DISPATCH();

# HALT: // Terminate

| Code Stream | Switch dispatch with single | Threaded dispatch with indi- |  |

|-------------|-----------------------------|------------------------------|--|

|             | BTB entry.                  | vidual BTB entry.            |  |

| start: A    | goto                        | A                            |  |

| В           | A                           | goto                         |  |

| A           | В                           | A                            |  |

| goto start  | A                           | В                            |  |

TABLE 3.1. Prediction result of different dispatch methods with BTB

targets correctly as no two consecutive instructions are the same. However, in a threaded dispatch where each operation has its own BTB entry, the prediction accuracy increases dramatically. For example, since *goto* and *B* both have their own BTB entries and they are always followed by *A*, the predictions for them are always correct in each iteration.

However, implementing threaded dispatch in a modern high-level language can be troublesome. The most standard way of jumping to a dynamic program address in an imperative language is by using function pointers or a similar mechanism. The downside of this method is that it introduces new instructions on program stack when jumping to/returning from the function call. Another standard solution in C/C++ is to use goto statement and label-as-value extension in GNU C (Listing 4), but this brings a new portability issue when target machine only has ANSI C.

#### **3.5.4 Indirect Threaded Dispatch**

Dewar introduced indirect threaded dispatch or indirect threaded code (ITC) as a more memory-efficient version of threaded dispatch (Dewar, 1975). Instead of having the code stream as an array of program address (8 bytes), it creates an address table and having integer offsets (4 bytes) as an array representing their position in the address table as shown in Listing 5. When targeting on a 64-bit machine in C, this typically means we can save about 4 bytes for each opcode depends on the design of the instruction set.

```

Listing 5 Example code for indirect threaded dispatch.

#define DISPATCH() goto **addressTable[code[ip++]]

// addressTable = [&&ADD, &&SUB, &&HALT];

// code = [0, 1, ...];

DISPATCH();

ADD:

// Computation goes here

DISPATCH();

SUB:

// Computation goes here

DISPATCH();

HALT:

// Terminate

```

Standard implementation is to use the goto statement and label-as-value extension in GNU C. Although it still has a portability issue, a surprising advantage of ITC regarding software engineering concern is that, it provides an easy way of switching between central dispatch and indirect threaded dispatch when target machine does not support the latter. Since Enum type used in switch dispatch can be treated as an integer type and therefore can be directly used as the offset in ITC; switching between ITC and switch dispatch can be done by using a few lines of macro as shown in Listing 6. In fact, many modern interpreters such as CPython relies on this technique to maintain probability while aiming for better performance. In contrast to direct threaded code, when the targeted machine does not support the GNU extension, it usually requires the interpreter author with a more sophisticate method to fall back to central dispatch, since the code stream required by two dispatch methods has fundamentally different types in language like C (Pointer v.s. Integer).

Listing 6 Switching between switch / threaded dispatch

```

#ifdef LABEL_AS_VALUE

#include addressTable.h

#define DISPATCH() goto **addressTable[code[ip++]]

#define OPEATION(op) op : LABEL_##op

#else

#define DISPATCH() ip++; break

#define OPERATION(op) op

#endif

while (true) {

switch(opCode) {

case OPERATION(ADD) : {

// Computation goes here

DISPATCH();

}

case OPERATION(SUB) : {

// Computation goes here

DISPATCH();

}

}

}

```

#### 3.5.5 Subroutine Threaded

Subroutine threaded was first described by Curely (Curley, 1993), who presented a Forth implementation on 68000CPU. In general, the idea of subroutine threaded is to 'glue' the instruction body with assembly code 'call' and 'return'; instead of dispatching based on a dynamic program address, code stream is loaded as a sequence of native function calls and directly to the corresponding instruction.

Subroutine threaded can reduce most of the indirect jump during the dispatches (Berndl et al., 2005), except for those relies on runtime result, such as virtual branches instruction. Although subroutine threaded involves machine dependent code, which can bring up a portability issue, the complexity of the code is well contained since it only involves porting native call and return instruction. Therefore, adding support for other platform is still relatively easy compared to porting a compiler.

## **3.6 Instruction Optimization**

So far the optimizations we have covered were all focusing on the dispatch loop itself; another approach would be to directly alter the instruction design in order to reduce number of dispatches.

| Code Stream | Prediction result | Code Stream with Superinstruction | Prediction result |

|-------------|-------------------|-----------------------------------|-------------------|

| start: A    | goto              | start: A_B_C                      | goto              |

| В           | A                 |                                   |                   |

| C           | В                 |                                   |                   |

| goto start  | C                 | goto start                        | $A\_B\_C$         |

| TABLE 3.2. | Superinstruction | with switch dis | spatch and BTB |

|------------|------------------|-----------------|----------------|

|------------|------------------|-----------------|----------------|

#### 3.6.1 Super-instruction

Intuitively, the less instruction we have in the program, the less branch indirection we could encounter and hence results in fewer misprediction penalty.

Ertl and Gregg (Ertl and David, 2003) came up with the idea of super-instruction, which reduce the number of dispatches needed for the same program by building specialized super-instruction that is made up of many small instructions. As an example shown in Table 3.2, if we have a large instruction that semantically equivalent to execute A, B and C in the order, we can reduce the number mispredictions from four to two for each iteration of the loop.

If one wants to build super-instruction statically, this typically would require the author to identify frequent sequences in the program, usually with a profile-guarded approach. Nevertheless, building super-instruction dynamically is similar to applying virtual instruction threaded code; it provides more opportunities for combing basic instructions but introduces a probability issue as it involves embedded assembly code. Finally, Ertl and Gregg also found that abusing the super-instruction would result in a growth in the opcode size and can be harmful on 32-bit machines.

#### 3.6.2 Selective Inlining

Selective inlining presented by Piumarta and Riccardi (Piumarta and Riccardi, 1998) is the most aggressive optimization technique that targets on reducing dispatch number. The idea is to translate the whole virtual program into one single instruction by concatenating each individual virtual body together. This does not require the author to generate assembly code for any interpreter instruction; it is instead done by 'memcpy'ing the machine code of each instruction body during runtime. The exact address to be copied can be determined at runtime by using GNU's label-as-value extension.

However, to keep the program counter (PC) correct, selective inlining can not deal with any relative jump to a function call, this means any instruction body with function call can not be inlined without

carefully inspect the source code. Since hardware architecture and compiler tend not to enforce any standard on whether a relative or absolute jump should be preferred, this makes selective inlining much more complicated; its portability does not depend on a particular standard which interpreter author can reference, but depends on a specific compiler implementation of a particular version. However, selective inlining can still be reliable for a virtual instruction set with fine-grained opcodes, where implementation is straightforward and does not involve many system calls.

## 3.6.3 Replication

Ertl and Gregg introduced replication along with super-instruction (Ertl and David, 2003). The optimization is done by duplicate each instruction body several times and uses different copies in different places of the code stream. In the extreme case, if every opcodes in the code stream can be duplicated, then each opcode will have its own jump location and can always be predicted correctly with BTB and threaded code.

Consider the example given in table 3.3 where prediction accuracy rate goes from 50% to 100% with the help of replication.

| Code Stream | Prediction without | Code Stream with      | Prediction result |

|-------------|--------------------|-----------------------|-------------------|

|             | replication        | Replication           | with replication  |

| start: A    | A                  | start: A <sub>1</sub> | $A_1$             |

| В           | goto               | В                     | В                 |

| A           | A                  | $A_2$                 | $A_2$             |

| goto start  | В                  | goto start            | goto              |

TABLE 3.3. Replication with BTB and threaded code

However, if one chooses the inappropriate instruction to replicate, it can hurt the prediction as shown in 3.4; a sub-optimal instruction B is chosen to be replicated, where overall accuracy goes from 66.67% to 50%. To ensure for the best performance, one should replicate every opcode in the code stream by using dynamic replication, with careful analysis during code generation and use 'memcpy' to copy the body of the instruction similar as selective inlining.

#### 3.7 OTHER RELATED WORK

| Code Stream | Prediction without | Code Stream with | Prediction result |

|-------------|--------------------|------------------|-------------------|

|             | replication        | Replication      | with replication  |

| start: A    | A                  | start: A         | A                 |

| В           | goto               | $B_1$            | goto              |

| A           | A                  | A                | A                 |

| В           | В                  | $B_2$            | $B_1$             |

| A           | A                  | A                | A                 |

| goto start  | В                  | goto start       | $B_2$             |

TABLE 3.4. Replication resulting in increasing misprediciton

# 3.7 Other Related Work

## **3.7.1 Instruction Reordering**

Brunthaler (Brunthaler, 2011) described an optimization approach by reordering the VM instruction in the instruction table, such that more frequent instructions can be successfully stored in cache level. This data-driven approach requires the writer to pre-analyze the instructions frequency in a particular VM and order the instructions accordingly. The author manage to show a factor of 1.142 speedups when experimented on Python using the *fasta* benchmark.

## 3.7.2 Code Generator for Interpreter

Another way to implement efficient VM is to use a code generator that automatically generates a stackbased interpreter for the programmer. Vmgen (Ertl et al., 2002) generates C code for the interpreter, just like how Yacc generates the parser. A significant advantage of using Vmgen is for the ease of implementation. More attracting, Vmgen applies complex optimization which usually hard for a programmer to write, such as super-instruction and replicate. In addition to that, Vmgen also supports scheduling and prefetching the VM instruction that targeting specific hardware architectures, such as PowerPC, which result in a 1.2 speed up. Experiment on GForth indicates that interpreter generated by Vmgen is faster and easier to implement than a hand-written interpreter, and only slower than the native code compiler by a factor of 2. However, machine-generated source code can be hard for a human to read and extend, and it adds the generator tool as an extra dependency for the interpreter implementation. Interpreter author may prefer to rely on the host language that has large community support from both academic and industry instead of a relatively small project with only a handful maintainers. That being said, the generated code from Vmgen can still be a good guideline for interpreter author to reference.

# 3.8 Modern Branch Predictor

The literature that is targeting on VM dispatch techniques all have one solid assumption: indirect jumps in VM interpreter are hard to be predicted. Although the assumption was valid given simple branch predictor back the time, the most recent research given by Rohou et al. (Rohou et al., 2015) offers a different opinion. They considered three interpreters (Python, Javascript, CLI) on a state-of-art branch predictors ITTAGE and three most recent Intel process generations in 2015. Their result indicates that the branch misprediction rate drop dramatically from 12 - 20 MPKI to an only 0.5 - 2 MPKI as the process evolved. In addition to that, the penalty of mispredictions has also decreased by a considerable amount — the number of instruction slots wasted due to branch misprediction drop from 14.5% on Sandy Bridge to 7.8% on Haswell.

Their finding may suggest that the dispatch optimisation techniques are no longer be effective on modern hardware. We were able to find few discussions about this paper in the language implementation community, but unfortunately, we were not able to find any formal research following up to this paper regarding the interpreter performance.

# 3.9 Chapter Summary